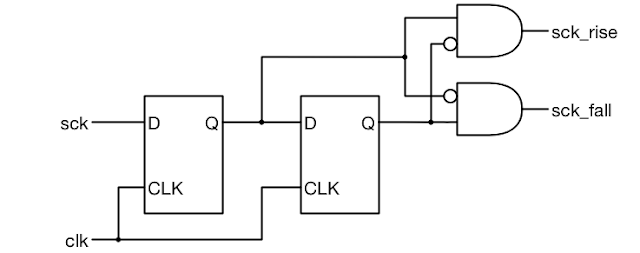

These digital elements are substituted with logical cells that belong to a real cell library for a given technology node. It can be seen that the one clock delay is implemented using a DFF and the output of the flip flop is wired to the input of an AND gate through an inverter. The behavioral model in Verilog was synthesized using Xilinx Vivado FPGA design tool and the hardware schematic has been generated as shown below. Basic design stimulus is written within the initial block which makes the simulator advance in time and drive the design with specific values appropriately. Instantiate the design in TB and connect with signals in TBĬlock for our design is generated by the always block which toggles clk every 5 time units, there by generating a clock with period = 10 time units. Reg clk // Declare internal TB signal called clk to drive clock to the design Reg sig // Declare internal TB signal called sig to drive the sig pin of the design The testbench simply holds our design and provides us a way to send in signals as inputs and observe the outputs to make sure that it operates as required. In order to simulate our design, we have to place the module of our verilog code inside a testbench. The expression simply takes sig and does a logical AND with the inversion of sig. Hence we have used the assign statement to assign an expression to pe.

Output pe is an implicit variable of type wire and can be assigned only by a continous assignment. We create an internal signal called sig_dly of type reg that can store a single clock cycle delayed version of sig, and is achieved by the always block. So we expect to see a pulse on pe whenever sig changes from value 0 to 1. The design aims to detect the positive edge of input sig, and output pe. The module shown above is named pos_edge_det and has two inputs and one output. Assign statement assigns the evaluated expression in the RHS to the internal net pe Combinational logic where sig is AND with delayed, inverted version of sig This always block ensures that sig_dly is exactly 1 clock behind sig Reg sig_dly // Internal signal to store the delayed version of signal Output pe) // Output signal that gives a pulse when a positive edge occurs Module pos_edge_det ( input sig, // Input signal for which positive edge has to be detected The idea behind a positive edge detector is to delay the original signal by one clock cycle, take its inverse and perform a logical AND with the original signal.

A positive edge detector will send out a pulse whenever the signal it is monitoring changes from 0 to 1 (positive edge).

0 kommentar(er)

0 kommentar(er)